Estació de retreball BGA òptica automàtica

Àmpliament utilitzat en la reparació a nivell de xip per a la placa base de mòbils, ordinadors portàtils, ordinadors, TV, aire condicionat, etc. Té una alta taxa d'èxit de reparació i un alt grau d'automatització i estalvia molts esforços humans. Som fabricants professionals d'aquesta màquina i tenim aquestes màquines disponibles en estoc.

Descripció

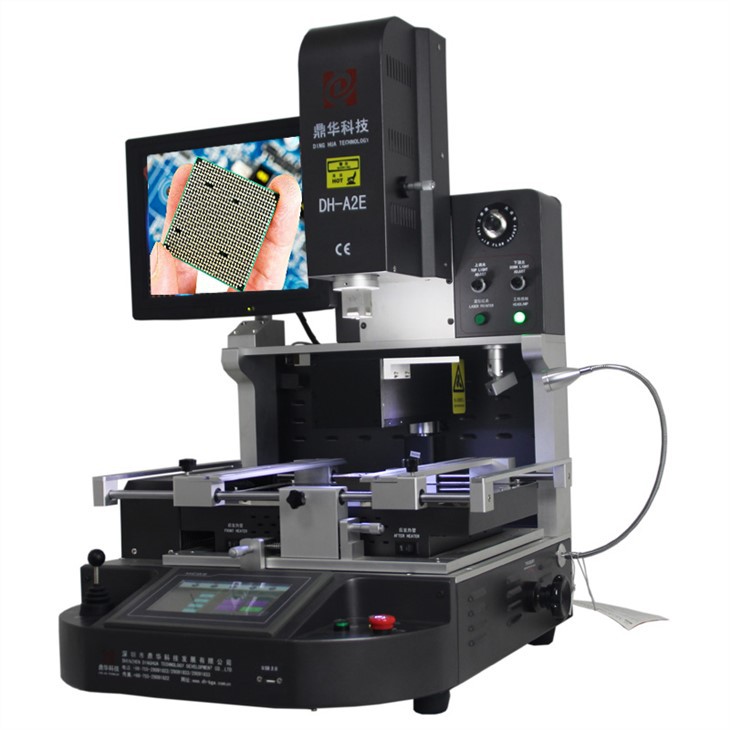

Estació de retreball BGA òptica automàtica

1.Aplicació de l'estació de retreball BGA òptica automàtica

Placa base d'ordinador, telèfon intel·ligent, ordinador portàtil, placa lògica MacBook, càmera digital, aire condicionat, TV i altres dispositius electrònics

equips de la indústria mèdica, indústria de la comunicació, indústria de l'automòbil, etc.

Adequat per a diferents tipus de xips: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, xip LED.

2. Característiques del producte de l'estació de retreball BGA òptica automàtica

•Alta taxa d'èxit de reparació a nivell de xip. El procés de desoldar, muntar i soldar és automàtic.

• L'alineació precisa de cada unió de soldadura es pot garantir amb la càmera CCD d'alineació òptica.

•Es pot assegurar un control precís de la temperatura amb 3 zones de calefacció independents. La màquina pot configurar i desar

1 milió de perfil de temperatura.

• El buit incorporat al capçal de muntatge recull el xip BGA automàticament després de completar la desoldació.

3.Especificació de l'estació de retreball BGA òptica automàtica

4.Detalls de l'estació de retreball BGA òptica automàtica

Càmera CCD (sistema d'alineació òptica precisa); 2. Pantalla digital HD; 3. Micròmetre (ajustar l'angle del xip);

4.3 escalfadors independents (aire calent i infrarojos); 5. Posicionament làser; 6. Interfície de pantalla tàctil HD, control PLC;

7. Far led; 8. Control del joystick.

5.Per què triar la nostra estació de retreball BGA òptica automàtica?

6.Certificat d'estació de retreball BGA òptica automàtica

7.Embalatge i enviament de l'estació de retreball BGA òptica automàtica

8.Preguntes freqüents

Com provar el xip?

Prova inicial de xip a nivell de sistema

El SoC es basa en processos profunds submicrònics, de manera que provar nous dispositius Soc requereix un enfocament completament nou. Perquè cada component funcional

té els seus propis requisits de prova, l'enginyer de disseny ha de fer un pla de proves al principi del procés de disseny.

S'ha d'implementar el pla de proves bloc per bloc per als dispositius SoC: eines ATPG degudament configurades per a proves lògiques; temps de prova curts; nova alta velocitat

models d'error i proves de memòria múltiple o matriu petita. Per a la línia de producció, el mètode de diagnòstic no només troba la falla, sinó que també separa

node defectuós del node de treball. A més, les tècniques de multiplexació de proves s'han d'utilitzar sempre que sigui possible per estalviar temps de prova. En l'àmbit de l'alta

Les proves d'IC integrats, les tècniques de disseny comprovables d'ATPG i IDDQ tenen un potent mecanisme de separació de fallades.

Altres paràmetres reals que s'han de planificar amb antelació inclouen el nombre de pins que cal escanejar i la quantitat de memòria a cada extrem.

Les exploracions de límits es poden incrustar al SoC, però no es limiten a proves d'interconnexió a plaques o mòduls multixip.

Tot i que la mida del xip està disminuint, un xip encara pot empaquetar milions a 100 milions de transistors i el nombre de modes de prova ha augmentat fins a un nivell sense precedents.

nivells, donant lloc a cicles de prova més llargs. Aquest problema es pot provar. Mode de compressió per resoldre, la relació de compressió pot arribar al 20% al 60%. Per a la gran escala d'avui

disseny del xip, per evitar problemes de capacitat, cal trobar programari de prova que es pugui executar en sistemes operatius de 64-bits.

A més, el programari de prova s'enfronta a nous problemes de prova causats per processos profunds de submicres i una freqüència creixent. En el passat, el mode de prova ATPG per

provar errors de bloqueig estàtics ja no era aplicable. L'addició de patrons funcionals a les eines tradicionals va fer difícil trobar nous errors. Un millor enfocament és

classifiqueu els grups de modes funcionals anteriors per determinar quines fallades no es poden detectar i, a continuació, creeu un mode ATPG per capturar aquests tipus d'errors que falten.

A mesura que augmenta la capacitat de disseny i disminueix el temps de prova per transistor, per trobar problemes relacionats amb la velocitat i verificar la temporització del circuit, un mètode de prova síncron

s'ha d'emprar. Les proves sincròniques han d'incorporar diversos models d'error, inclosos models transitoris, retards de ruta i IDDQ.

Algunes empreses del sector creuen que la combinació d'errors de bloqueig, funcionals i transitoris/de retard pot ser l'estratègia de prova més eficaç. Per profund

Els xips submicrons i el funcionament d'alta freqüència, les proves de retard de transitori i de recorregut són encara més importants.

Per resoldre el problema de la precisió ATE en sincronitzar el nucli de prova i reduir el cost, cal trobar un nou mètode que simplifiqui la interfície de

el dispositiu de prova (la prova de retard de transitori i camí requereix un rellotge precís a la interfície del dispositiu de prova), garanteix que el senyal sigui prou precís durant la prova.

Com que hi ha una gran possibilitat de defectes de fabricació al bloc de memòria SoC, la memòria BIST ha de tenir una funció de diagnòstic. Un cop trobat un problema,

la unitat d'adreces defectuosa es pot assignar a la memòria redundant de la unitat d'adreces de recanvi i l'adreça d'error detectada es descartarà. Eviteu descartar

tot el xip car.

La prova de petits blocs de memòria incrustats elimina la necessitat de portes addicionals o lògica de control. Per exemple, les tècniques de prova de conversió de vectors poden convertir

modes funcionals en una sèrie de modes d'escaneig.

A diferència del mètode BIST, l'entrada funcional del bloc de memòria bypass no requereix lògica addicional. Com que no es requereix cap lògica de prova addicional, SoC

els enginyers de desenvolupament poden reutilitzar els patrons de prova que es van formar en el passat.

Les eines ATPG avançades no només proveen macros en paral·lel, sinó que també determinen si hi ha conflictes, així com detallen quines macros es poden provar en paral·lel i quines.

les macros no es poden provar en paral·lel. A més, aquestes macros es poden provar de manera efectiva fins i tot si el rellotge de macro és el mateix que el rellotge d'exploració (com ara la memòria síncrona).

Actualment, no hi ha prou punts de prova a la placa densa de doble cara i cada xip complex ha d'estar equipat amb un circuit d'exploració de límits. Sense

Les exploracions de límits, les cerques de defectes de fabricació a nivell de placa són bastant difícils i ni tan sols es poden trobar. Amb l'exploració de límits, les proves a nivell de tauler són extremadament fàcils

i independent dels circuits lògics dins del xip. L'exploració de límits també pot configurar el mode ATPG a la cadena d'escaneig del xip en qualsevol etapa de producció.