Compra BGA Rework Station

1. Podeu comprar BGA Rework Station directament del fabricant original.2. Estació de retreball BGA automàtica DH-A2.3. Micròmetre per ajustar l'angle BGA i ajustar la placa base.4. Port: Shenzhen.

Descripció

Compra BGA Rework Station

1.Aplicació de l'estació de retreball BGA òptica automàtica

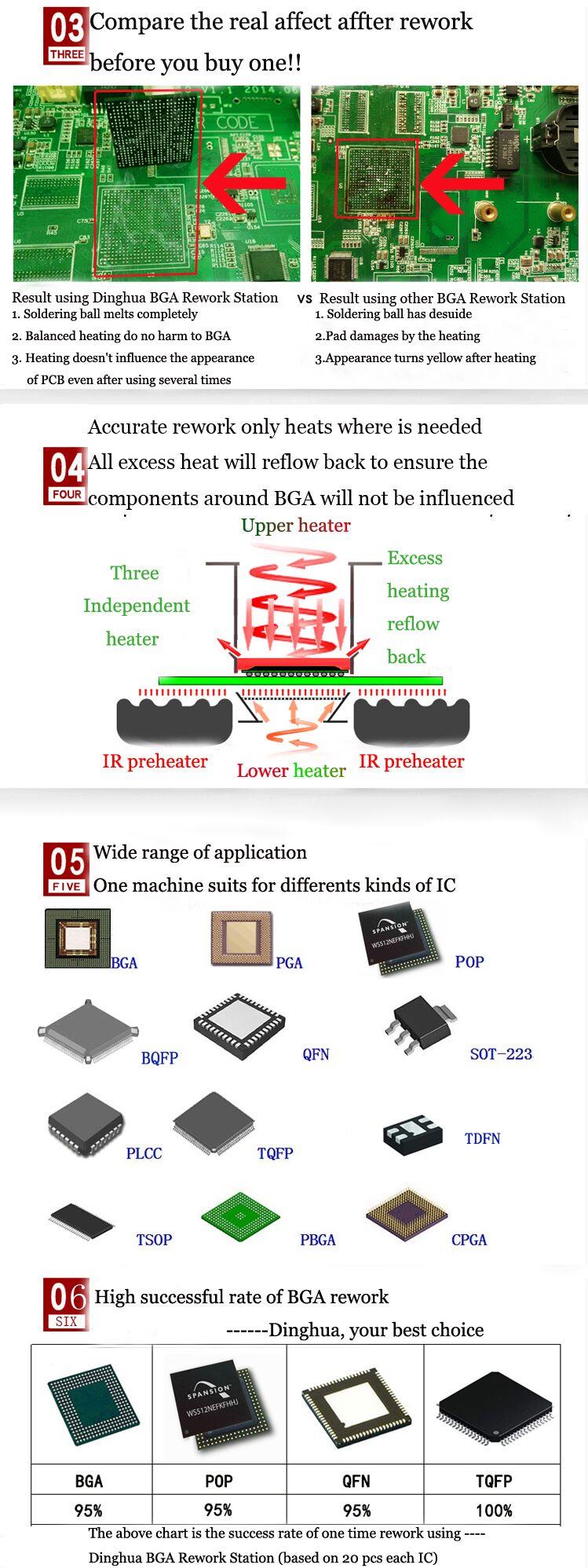

Treballa amb tot tipus de plaques base o PCBA.

Soldar, reballar, desoldar diferents tipus de xips: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP,

PBGA, CPGA, xip LED.

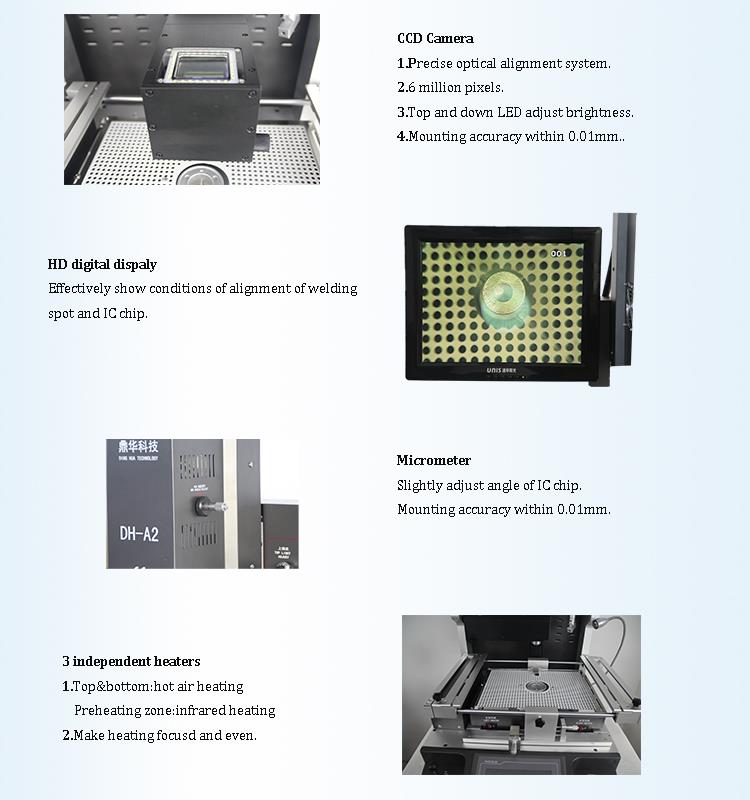

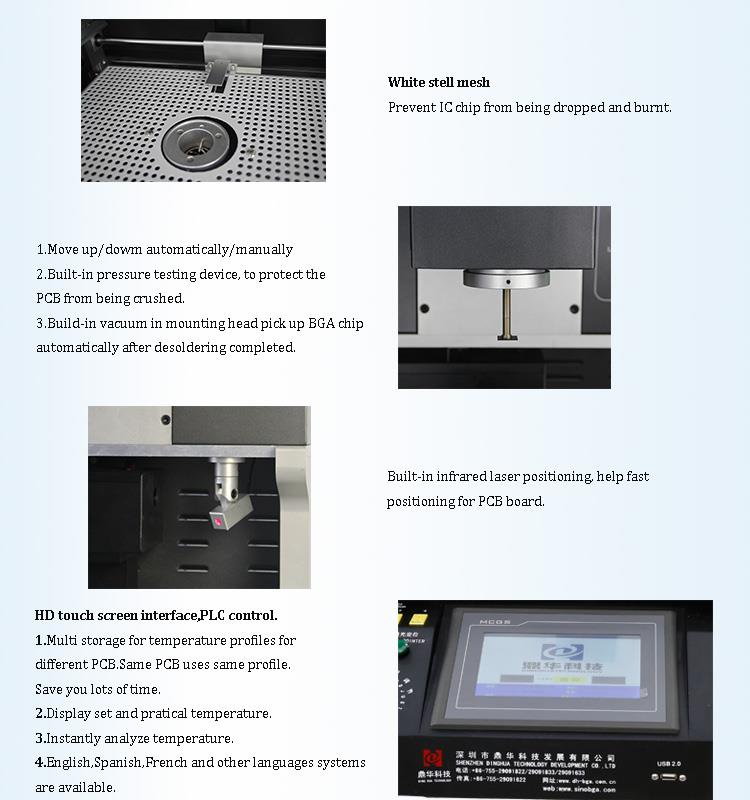

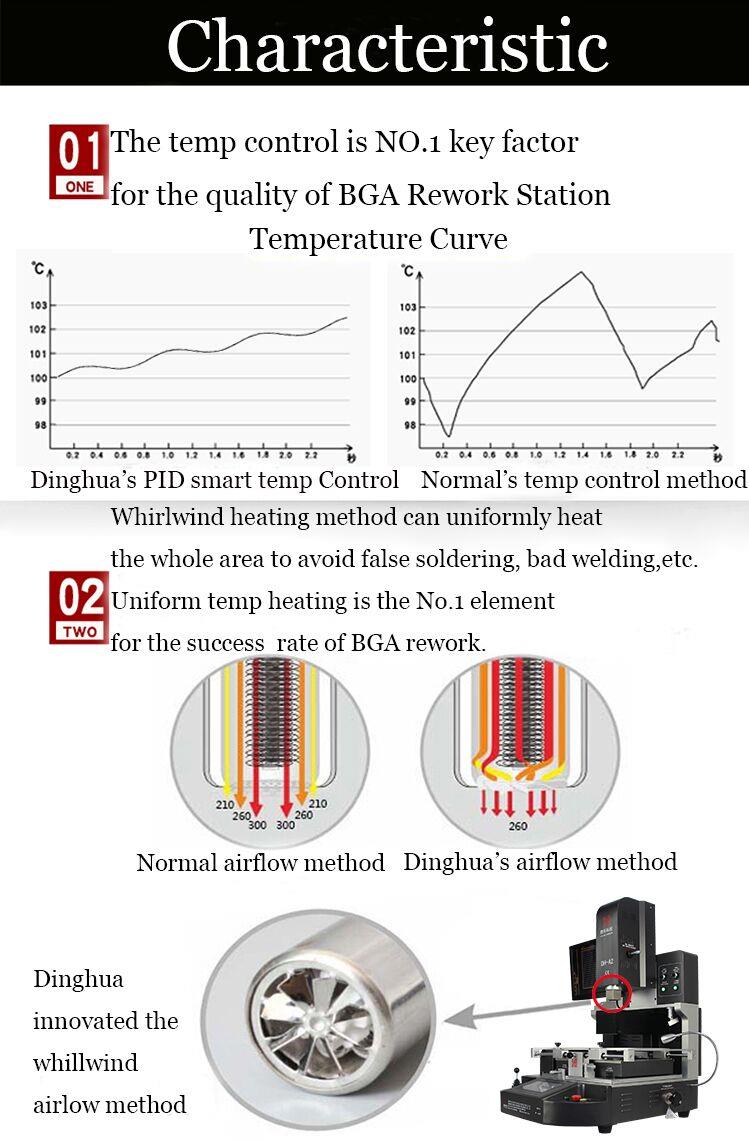

2. Característiques del producteÒptic automàticEstació de retreball BGA

3.Especificació deÒptic automàticEstació de retreball BGA

4.Detalls deÒptic automàticEstació de retreball BGA

5.Per què triar el nostreÒptic automàticEstació de retreball BGA?

6.Certificat deÒptic automàticEstació de retreball BGA

Certificats UL, E-MARK, CCC, FCC, CE ROHS. Mentrestant, per millorar i perfeccionar el sistema de qualitat,

Dinghua ha aprovat la certificació d'auditoria in situ ISO, GMP, FCCA, C-TPAT.

7. Embalatge i enviament deAutomàticEstació de retreball BGA

8.Enviament perÒptic automàticMàquina de reballing BGA

DHL/TNT/FEDEX. Si voleu un altre termini d'enviament, digueu-nos-ho. Us donarem suport.

9. Condicions de pagament

Transferència bancària, Western Union, targeta de crèdit.

Si us plau, digueu-nos si necessiteu un altre suport.

10. Com funciona la màquina automàtica de reballadora DH-A2 BGA IC?

11. Coneixements relacionats

Sobre el xip flash

Dinàmica de l'oferta

Recentment, la nova empresa de xips propietari de SandForce, LSI, va dir que estan desenvolupant un nou firmware per al SSD mestre SF.

a Ultrabook. La funció principal és reduir el consum d'energia de l'SSD i també millorar-ne el rendiment

SSD i accelerar l'inici. velocitat.

paràmetre

3. Font d'alimentació de 3V;

La matriu de cèl·lules de memòria interna del xip és (256 M + 8.192 M) bit × 8 bits, i el registre de dades i la memòria intermèdia són tots dos

(2k + 64) bit × 8 bits;

Port d'E/S amb multiplexació d'instruccions/adreça/dades;

Les ordres de programació i d'esborrat es poden suspendre durant la conversió d'energia;

Gràcies a la tecnologia fiable de la porta mòbil CMOS, el xip pot aconseguir un cicle màxim de programa/esborrat de 100 kB, que

garanteix l'emmagatzematge de dades durant 10 anys sense pèrdua.

Estat de treball

E/S0~I/O7: port d'entrada i sortida de dades, el port d'E/S s'utilitza sovint per a l'entrada d'instruccions i adreça i entrada/sortida de dades,

on es troben les dades

Entra durant el procés de lectura. Quan el xip no està seleccionat o no es pot sortir, el port d'E/S es troba en un estat d'alta impedància.

CLE: el tancament d'instruccions s'utilitza per activar la instrucció al camí del registre d'instruccions i bloquejar la instrucció al

El front ascendent de WE i CLE és alt.

ALE: tancament de l'adreça, que s'utilitza per activar el camí de l'adreça al registre d'adreces interna, i l'adreça està bloquejada al

El front ascendent de WE i ALE és alt.

CE: Selector de xip, utilitzat per controlar la selecció del dispositiu. Quan el dispositiu està ocupat, CE és alt i ignorat, i el dispositiu no pot tornar

a l'estat d'espera.

RE: Habilitació de lectura, que s'utilitza per controlar la sortida contínua de dades i enviar les dades al bus d'E/S. Les dades de sortida només són vàlides a

la vora descendent de la RE i també pot acumular adreces de dades internes.

WE: El terminal d'habilitació d'escriptura s'utilitza per controlar l'escriptura d'instruccions del port d'E/S. Al mateix temps, l'ordre, adreça

i les dades es poden bloquejar a la vora ascendent del pols WE a través d'aquest port.

WP: protector d'escriptura, que es pot protegir contra escriptura en la conversió d'energia a través del terminal WP. Quan el WP és baix, és intern

el generador d'alt nivell es reiniciarà.

R/ B: sortida a punt/ocupat, la sortida de R/B pot mostrar l'estat de funcionament del dispositiu. Quan R/B és baix, indica que un programa,

L'operació d'esborrat o de lectura aleatòria està en curs. Un cop finalitzada l'operació, R/B tornarà automàticament al nivell alt. Des del

El terminal és una sortida de drenatge obert, no estarà en un estat d'alta impedància fins i tot quan el xip no estigui seleccionat o la sortida estigui desactivada.

PRE: operació de lectura d'encesa, que s'utilitza per controlar l'operació de lectura automàtica quan està encès, i es pot connectar el terminal PRE

a VCC per realitzar l'operació de lectura automàtica d'encesa.

VCC: terminal d'alimentació del xip.

VSS: Mòlta d'encenall.

NC: Penjant.

Edició de l'estat del treball

Operació de lectura d'1 pàgina

L'estat predeterminat del xip flash és l'estat de lectura. L'operació de lectura consisteix a iniciar la instrucció escrivint l'adreça 00h al

registre d'instruccions a través de 4 cicles d'adreces. Un cop bloquejada la instrucció, l'operació de lectura no es pot escriure a la pàgina següent.

Les dades es poden emetre aleatòriament des d'una pàgina escrivint una instrucció de sortida de dades aleatòries. L'adreça de dades es pot trobar automàticament

la següent adreça mitjançant instruccions de sortida aleatòries de l'adreça de dades a sortir. Les operacions de sortida de dades aleatòries es poden utilitzar múltiples

vegades.

Programació de 2 pàgines

La programació del xip flash és pàgina per pàgina, però admet programació de pàgines parcials múltiples en un sol cicle de programació de pàgina,

mentre que el nombre de pàgines consecutives d'una pàgina parcial és 2112. L'operació del programa es pot iniciar escrivint al programa de pàgines.

instrucció de reconeixement (10h), però s'han d'introduir dades contínues abans d'escriure la instrucció (10h).

Càrrega contínua de dades Després d'escriure una instrucció d'entrada de dades contínua (80 h), iniciarà 4 cicles d'entrada d'adreces i càrrega de dades, però

la paraula és diferent de les dades programades, no cal carregar-la. El xip admet l'entrada aleatòria de dades a la pàgina i pot

canvieu automàticament l'adreça segons l'ordre d'entrada de dades aleatòries (85 h). L'entrada de dades aleatòria també es pot utilitzar diverses vegades.

3 programació de memòria cau

La programació de la memòria cau és un tipus de programació de pàgines que es pot realitzar mitjançant un registre de dades de 2112-byte i només és vàlida en un bloc. Perquè

el xip flash té una memòria intermèdia de pàgina, pot realitzar una entrada de dades contínua quan el registre de dades està programat a la cel·la de memòria. Memòria cau

la programació només pot començar després del final d'un cicle de programació incomplet i els registres de dades es passen de la memòria cau. La programació interna es pot jutjar pel pin R/B. Si el sistema només utilitza R/B per supervisar el progrés del programa, llavors l'ordre de l'última pàgina

del programa de destinació s'han d'organitzar segons les instruccions de programació de la pàgina actual.

Doblatge de 4 unitats d'emmagatzematge

Aquest efecte pot sobreescriure de manera ràpida i eficient les dades d'una pàgina sense accedir a la memòria externa. Des del temps dedicat en continu

s'escurça l'accés i la recàrrega, es millora la capacitat d'execució del sistema. Sobretot quan s'actualitza una part del bloc i

la resta del bloc s'ha de copiar al bloc nou, els seus avantatges es mostren clarament. Aquesta operació és una ordre de lectura executada contínuament,

però no requereix accés continu i còpia del programa des de l'adreça de destinació. Una operació de lectura de l'adreça de la pàgina original

La instrucció "35h" pot transferir els 2112 bytes de dades sencers al buffer de dades intern. Quan el xip torna a l'estat llest, la pàgina es copia

S'escriu la instrucció d'entrada de dades amb el bucle d'adreça de destinació. El programa d'error en aquesta operació ve donat per l'estat "aprovat/fallat". Malgrat això,

si l'operació triga massa a executar-se, es produirà un error d'operació de bits a causa de la pèrdua de dades, donant lloc a un error extern "comprovar/corregir" la comprovació del dispositiu

fracàs. Per aquest motiu, l'operació s'ha de corregir amb dos errors.

Esborrat de 5 blocs

L'operació d'esborrat del xip flash es realitza per blocs. La càrrega de l'adreça de bloc començarà amb una instrucció d'esborrat de bloc i es completarà en dos cicles. De fet, quan les línies d'adreces A12 a A17 es queden flotants, només estan disponibles les línies d'adreces A18 a A28. L'esborrat es pot iniciar carregant l'ordre de confirmació d'esborrat i l'adreça de bloqueig. Aquesta operació s'ha de realitzar en aquest ordre per evitar que el contingut de la memòria es vegi afectat per soroll extern i provoqui un error d'esborrat.

6 estat de lectura

Un registre d'estat dins del xip flash confirma que el programa i les operacions d'esborrat s'han completat correctament. Després de la instrucció d'escriptura (70 h) al registre d'instruccions, el cicle de lectura envia el contingut del registre d'estat a l'E/S del front descendent de CE o RE. El registre d'instruccions romandrà en estat de lectura fins que arribi la nova instrucció, de manera que si el registre d'estat es troba en estat de lectura durant un cicle de lectura aleatòria, s'ha de donar una instrucció de lectura abans que comenci el cicle de lectura.